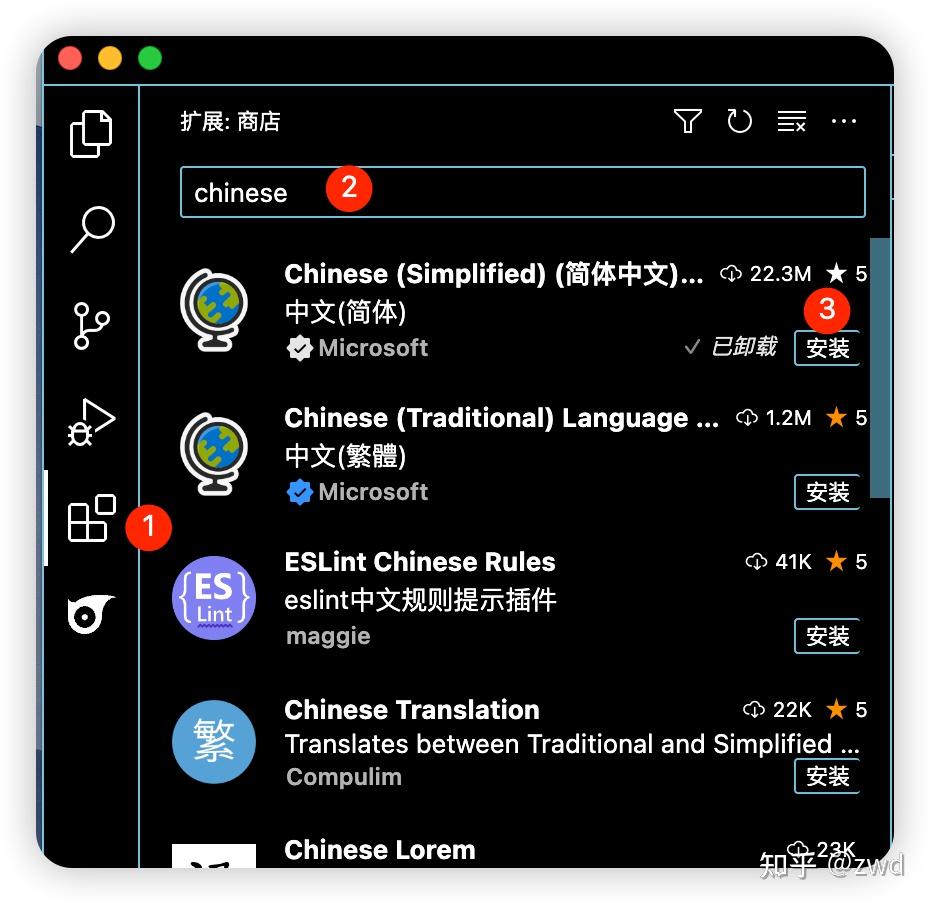

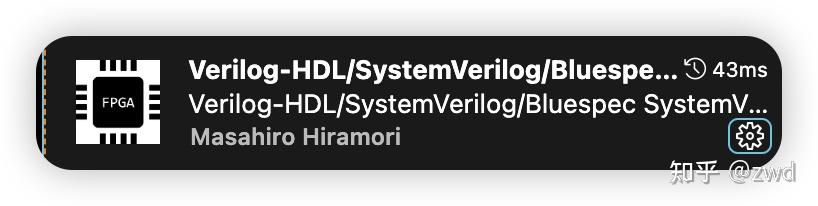

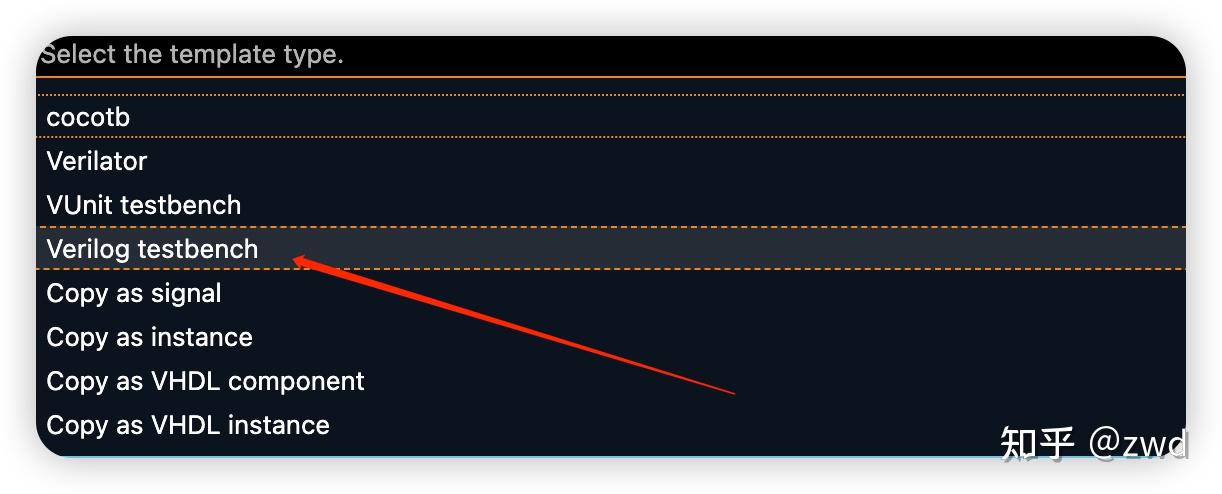

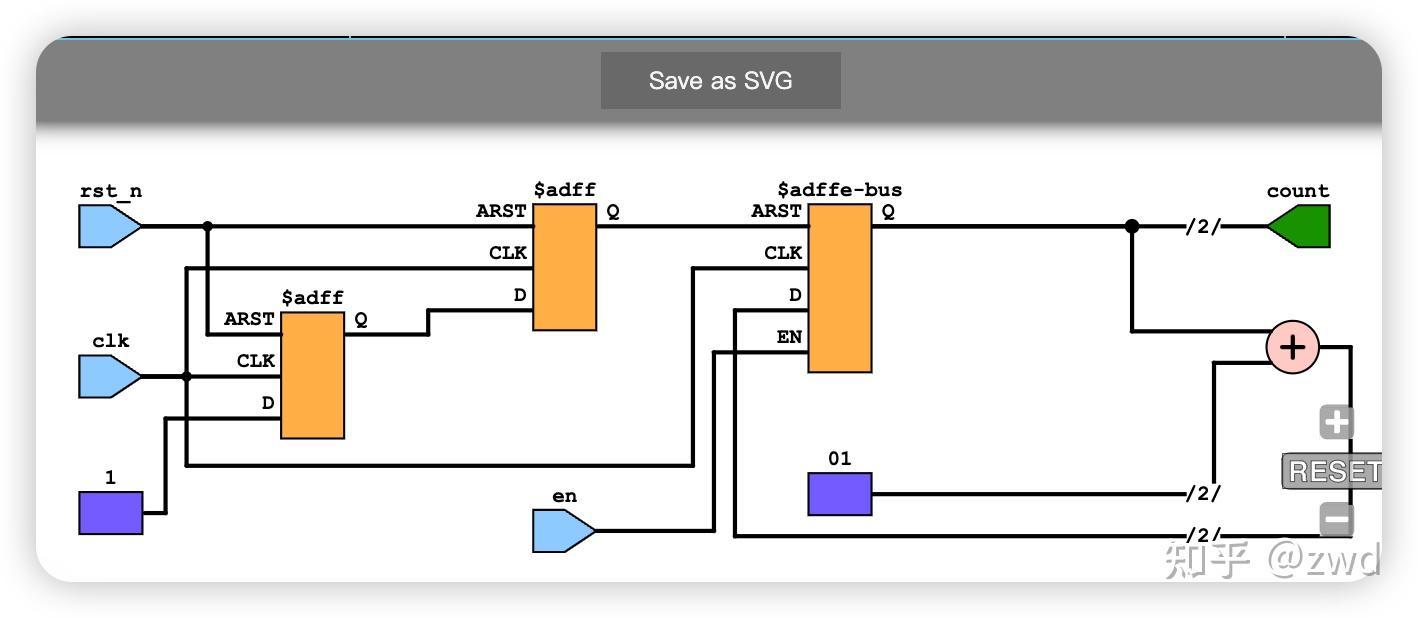

VS Code丰富的插件可以加快verilog书写速度,提高电路设计效率。 效果演示:分别演示了moudle、always块 快速书写(下文含配置方法及本人配置代码);文档自动生成、电路图生成、自动例化和tb生成(电路图生成十分适合初学者理解代码)  https://www.zhihu.com/video/1628730166280081408 一、安装插件方法 以安装chinese插件为例,3步安装后插件自动生效。  VS安装插件 二、verilog相关插件:主要介绍两个插件verilog HDL 和 TerosHDL 插件1verilog HDL :主要使用其代码片段补全功能  verilog HDL 代码补全功能的个人配置,打开verilog.json文件, 根据自己需要去配置。路径如下:  修改配置路径 例子1: 修改always前缀(博主配置供参考) 在verilog.json文件中修改如下,其中$1作用是按tab键自动跳转变量: "always zwd": {"prefix": ["alw", "always"], "body": [ "always @(posedge clk negedge rst_n) ", "begin", "\tif(rst_n) begin", "\t\t${1:reg1}<=0;", "\tend else if(${2:reg2}==)", "\tbegin", "\t\t${1:reg1}<=", "\tend", "end" ], "description": "Insert an always block" }, 输入"alw", "always"会出现  always 代码块 修改后必须重启vs code !! 例子2: 在verilog.json文件中修改module, "module zwd": { //一个名称提示"prefix": "module", //真正输入的前缀 "body": [ "module ${1:moduleName} (", //第1个变量,输入module后会自动跳转,按tab跳转到2 "input wire clk", "input wire rst_n", "output reg ", ");", "\t$0", "reg [] \t${2:reg1};", //第2个变量,下面出现2的地方会同时改变 "always @(posedge clk negedge rst_n) ", "begin", "\tif(!rst_n) begin", "\t\t${2:reg1}<=0;", "\tend else if()", "\tbegin", "\t\t${2:reg1}<=;", "\tend", "end", "endmodule" ], "description": "Insert a module zwd" }, 输入一个module后会出现。和上面代码对应学习  moudle的配置 b站视频推荐: 【推荐】写代码也可以很享受——基于VS Code的Verilog编写环境搭建_哔哩哔哩_bilibili 插件2:Teros HDL :十分强大!强推! 功能1、模块例化、testbench生成,该插件自带高亮功能很好看。 安装完成后右上角会出现下图 ,点击选择  功能选择  选择instance 选择instance 然后将例化粘贴在需要的位置。 testbench同理,选择后粘贴即可。  选择testbench 功能2、找信号定义:ctrl+鼠标左键 功能3、生成电路图和自动生成文档!!!!最强大的功能  自动生成电路图  自动生成文档 以上两个功能配置方法如下: 1、安装pyhton,建议默认路径 2、vscode的终端下安装 teroshdl  3、按照下图设置后重启  遇到问题找官网 https://terostechnology.github.io/terosHDLdoc/documenter/configuration.html |

![]() 万奢网手机版

万奢网手机版

官网微博:万奢网服务平台